#### PLCM Assignment 2 (6th Sem. EE)

- Q. 1 What is difference between microcontroller and microprocessor?

- Q. 2 Draw and explain the functions of block diagram of PIC microcontroller.

- Q. 3 Draw and explain pin diagram of PLC.

- Q. 4. Draw block diagram of 8051 microcontroller.

- Q. 5 Write short note on memory organisation of 8051.

#### Assignment 3 (6th Sem. EE)

- Q. 1 Design and explain 7-segment interface.

- Q. 2 Explain the LCD interfacing with 8051.

- Q. 3 Write steps to execute the assembly language program.

- Q. 4 Write a short note on embedded system.

- Q. 5 Explain 8051 instruction set and its five types.

#### PLCM Seminar Topics (Jan-May 2020)

| S. No. | Seminar Topic                                       | Roll No.          |  |

|--------|-----------------------------------------------------|-------------------|--|

| 1.     | Block diagram & functions of PLC                    | 81-93             |  |

| 2.     | PLCs, Relays, Advantages, Manufacturers             | 94-105            |  |

| 3.     | PLCs instructions & Instruction-set                 | 106-118           |  |

| 4.     | Ladder diagram Programming                          | 119-129           |  |

| 5.     | 8051 Microcontroller, Architecture & working        | 130-140           |  |

| 6.     | Assembler, Interrupt, different types of Interfaces | 141-156, 2017/577 |  |

## **8051 Microcontroller Pin Diagram**

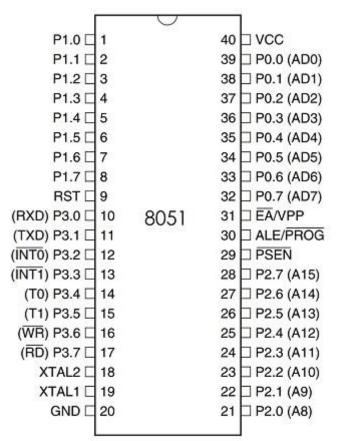

As mentioned in the previous tutorial, 8051 Microcontroller is available in a variety of packages like 40 – pin DIP or 44 – lead PLCC and TQFP. The pin orientation of an 8051 Microcontroller may change with the package but the Pin Configuration is same.

The following image shows the 8051 Microcontroller Pin Diagram with respect to a 40 – pin Dual In-line Package (DIP).

40 - PIN DIP

Since it is a 40 – pin DIP IC, each side contains 20 Pins. We have also seen that there other packages of 8051 like the 44 – Lead PLCC and the 44 – Lead TQFP. The following image shows the 8051 Microcontroller Pin Diagram for these packages specifically.

## **8051 Microcontroller Pin Description**

The Pin Description or Pin Configuration of the 8051 Microcontroller will describe the functions of each pins of the 8051 Microcontroller. Let us now see the pin description.

*Pins 1 – 8 (PORT 1):* Pins 1 to 8 are the PORT 1 Pins of 8051. PORT 1 Pins consists of 8 – bit bidirectional Input / Output Port with internal pull –

up resistors. In older 8051 Microcontrollers, PORT 1 doesn't serve any additional purpose but just 8 – bit I/O PORT.

In some of the newer 8051 Microcontrollers, few PORT 1 Pins have dual functions. P1.0 and P1.1 act as Timer 2 and Timer 2 Trigger Input respectively.

P1.5, P1.6 and P1.7 act as In-System Programming Pins i.e. MOSI, MISO and SCK respectively.

*Pin 9 (RST):* Pin 9 is the Reset Input Pin. It is an active HIGH Pin i.e. if the RST Pin is HIGH for a minimum of two machine cycles, the microcontroller will be reset. During this time, the oscillator must be running.

*Pins 10 – 17 (PORT 3):* Pins 10 to 17 form the PORT 3 pins of the 8051 Microcontroller. PORT 3 also acts as a bidirectional Input / Output PORT with internal pull-ups. Additionally, all the PORT 3 Pins have special functions. The following table gives the details of the additional functions of PORT 3 Pins.

| PORT 3 Pin | Function | Description           |

|------------|----------|-----------------------|

| P3.0       | RXD      | Serial Input          |

| P3.1       | TXD      | Serial Output         |

| P3.2       | INT0     | External Interrupt 0  |

| P3.3       | INT1     | External Interrupt 1  |

| P3.4       | ТО       | Timer 0               |

| P3.5       | T1       | Timer 1               |

| P3.6       | WR       | External Memory Write |

| P3.7       | RD       | External Memory Read  |

*Pins 18 & 19:* Pins 18 and 19 i.e. XTAL 2 and XTAL 1 are the pins for connecting external oscillator. Generally, a Quartz Crystal Oscillator is connected here.

*Pin 20 (GND):* Pin 20 is the Ground Pin of the 8051 Microcontroller. It represents 0V and is connected to the negative terminal (0V) of the Power Supply.

*Pins 21 – 28 (PORT 2):* These are the PORT 2 Pins of the 8051 Microcontroller. PORT 2 is also a Bidirectional Port i.e. all the PORT 2 pins act as Input or Output. Additionally, when external memory is interfaced, PORT 2 pins act as the higher order address byte. PORT 2 Pins have internal pull-ups.

*Pin 29 (PSEN):* Pin 29 is the Program Store Enable Pin (PSEN). Using this pins, external Program Memory can be read.

*Pin 30 (ALE/PROG):* Pin 30 is the Address Latch Enable Pin. Using this Pins, external address can be separated from data (as they are multiplexed by 8051).

During Flash Programming, this pin acts as program pulse input (PROG).

**Pin 31 (EA/VPP):** Pin 31 is the External Access Enable Pin i.e. allows external Program Memory. Code from external program memory can be fetched only if this pin is LOW. For normal operations, this pins is pulled HIGH.

During Flash Programming, this Pin receives 12V Programming Enable Voltage (VPP).

*Pins 32 – 39 (PORT 0):* Pins 32 to 39 are PORT 0 Pins. They are also bidirectional Input / Output Pins but without any internal pull-ups. Hence, we need external pull-ups in order to use PORT 0 pins as I/O PORT.

*Pin 40 (VCC):* Pin 40 is the power supply pin to which the supply voltage is given (+5V).

## **8051 Addressing Modes**

### What is an Addressing Mode?

An Addressing Mode is a way to locate a target Data, which is also called as Operand. The 8051 Family of Microcontrollers allows five types of Addressing Modes for addressing the Operands. They are:

- Immediate Addressing

- Register Addressing

- Direct Addressing

- Register Indirect Addressing

- Indexed Addressing

#### Immediate Addressing

In Immediate Addressing mode, the operand, which follows the Opcode, is a constant data of either 8 or 16 bits. The name Immediate Addressing came from the fact that the constant data to be stored in the memory immediately follows the Opcode.

The constant value to be stored is specified in the instruction itself rather than taking from a register. The destination register to which the constant data must be copied should be the same size as the operand mentioned in the instruction.

Example: MOV A, #030H

Here, the Accumulator is loaded with 30 (hexadecimal). The # in the operand indicates that it is a data and not the address of a Register.

Immediate Addressing is very fast as the data to be loaded is given in the instruction itself.

### Register Addressing

In the 8051 Microcontroller Memory Organization Tutorial, we have seen the organization of RAM and four banks of Working Registers with eight Registers in each bank.

In Register Addressing mode, one of the eight registers (R0 - R7) is specified as Operand in the Instruction.

It is important to select the appropriate Bank with the help of PSW Register. Let us see a example of Register Addressing assuming that Bank0 is selected.

Example: MOV A, R5

Here, the 8-bit content of the Register R5 of Bank0 is moved to the Accumulator.

### Direct Addressing

In Direct Addressing Mode, the address of the data is specified as the Operand in the instruction. Using Direct Addressing Mode, we can access any register or on-chip variable. This includes general purpose RAM, SFRs, I/O Ports, Control registers.

#### Example: MOV A, 47H

Here, the data in the RAM location 47H is moved to the Accumulator.

#### Register Indirect Addressing

In the Indirect Addressing Mode or Register Indirect Addressing Mode, the address of the Operand is specified as the content of a Register. This will be clearer with an example.

Example: MOV A, @R1

The @ symbol indicates that the addressing mode is indirect. If the contents of R1 is 56H, for example, then the operand is in the internal RAM location 56H. If the contents of the RAM location 56H is 24H, then 24H is moved into accumulator.

Only R0 and R1 are allowed in Indirect Addressing Mode. These register in the indirect addressing mode are called as Pointer registers.

### Indexed Addressing Mode

With Indexed Addressing Mode, the effective address of the Operand is the sum of a base register and an offset register. The Base Register can be either Data Pointer (DPTR) or Program Counter (PC) while the Offset register is the Accumulator (A).

In Indexed Addressing Mode, only MOVC and JMP instructions can be used. Indexed Addressing Mode is useful when retrieving data from look-up tables.

Example: MOVC A, @A+DPTR

Here, the address for the operand is the sum of contents of DPTR and Accumulator.

**NOTE:** Some authors and textbooks add few other Addressing Modes like Absolute Addressing Mode, Relative Addressing Mode and Long Addressing Mode.

Also read: 8051 MICROCONTROLLER ARCHITECTURE.

# Types of Instructions in 8051 Microcontroller Instruction Set

Before seeing the types of instructions, let us see the structure of the 8051 Microcontroller Instruction. An 8051 Instruction consists of an Opcode (short of Operation – Code) followed by Operand(s) of size Zero Byte, One Byte or Two Bytes.

The Op-Code part of the instruction contains the Mnemonic, which specifies the type of operation to be performed. All Mnemonics or the Opcode part of the instruction are of One Byte size.

Coming to the Operand part of the instruction, it defines the data being processed by the instructions. The operand can be any of the following:

- No Operand

- Data value

- I/O Port

- Memory Location

- CPU register

There can multiple operands and the format of instruction is as follows:

#### MNEMONIC DESTINATION OPERAND, SOURCE OPERAND

A simple instruction consists of just the opcode. Other instructions may include one or more operands. Instruction can be one-byte instruction, which contains only opcode, or two-byte instructions, where the second byte is the operand or three byte instructions, where the operand makes up the second and third byte.

Based on the operation they perform, all the instructions in the 8051 Microcontroller Instruction Set are divided into five groups. They are:

- Data Transfer Instructions

- Arithmetic Instructions

- Logical Instructions

- Boolean or Bit Manipulation Instructions

- Program Branching Instructions

We will now see about these instructions briefly.

# **Data Transfer Instructions**

The Data Transfer Instructions are associated with transfer with data between registers or external program memory or external data memory. The Mnemonics associated with Data Transfer are given below.

- MOV

- MOVC

- MOVX

- PUSH

- POP

- XCH

- XCHD

The following table lists out all the possible data transfer instruction along with other details like addressing mode, size occupied and number machine cycles it takes.

| Mnemonic     | Instruction      | Description                                | Addressing Mode | # of Bytes | # of Cycles |

|--------------|------------------|--------------------------------------------|-----------------|------------|-------------|

| MOV          | A, #Data         | A ← Data                                   | Immediate       | 2          | 1           |

|              | A, Rn            | A ← Rn                                     | Register        | 1          | 1           |

|              | A, Direct        | A ← (Direct)                               | Direct          | 2          | 1           |

|              | A, @Ri           | A ← @Ri                                    | Indirect        | 1          | 1           |

|              | Rn, #Data        | Rn ← data                                  | Immediate       | 2          | 1           |

|              | Rn, A            | Rn ← A                                     | Register        | 1          | 1           |

|              | Rn, Direct       | Rn ← (Direct)                              | Direct          | 2          | 2           |

|              | Direct, A        | (Direct) ← A                               | Direct          | 2          | 1           |

|              | Direct, Rn       | (Direct) ← Rn                              | Direct          | 2          | 2           |

|              | Direct1, Direct2 | (Direct1) ← (Direct2)                      | Direct          | 3          | 2           |

|              | Direct, @Ri      | (Direct) ← @Ri                             | Indirect        | 2          | 2           |

|              | Direct, #Data    | (Direct) ← #Data                           | Direct          | 3          | 2           |

|              | @Ri, A           | @Ri ← A                                    | Indirect        | 1          | 1           |

|              | @Ri, Direct      | @Ri ← Direct                               | Indirect        | 2          | 2           |

|              | @Ri, #Data       | @Ri ← #Data                                | Indirect        | 2          | 1           |

|              | DPTR, #Data16    | DPTR                                       | Immediate       | 3          | 2           |

| MOVC         | A, @A+DPTR       | A ← Code Pointed by A+DPTR                 | Indexed         | 1          | 2           |

|              | A, @A+PC         | A ← Code Pointed by A+PC                   | Indexed         | 1          | 2           |

|              | A, @Ri           | A ← Code Pointed by Ri (8-bit Address)     | Indirect        | 1          | 2           |

| MOVX         | A, @DPTR         | A ← External Data Pointed by DPTR          | Indirect        | 1          | 2           |

| CHECOTO COMO | @Ri, A           | @Ri ← A (External Data 8-bit Addr)         | Indirect        | 1          | 2           |

|              | @DPTR, A         | @DPTR ← A (External Data 16-bit Addr)      | Indirect        | 1          | 2           |

| DITOTI       | Dive             |                                            |                 | CTRONICS   |             |

| PUSH         | Direct           | Stack Pointer SP    (Direct)               | Direct          | 2          | 2           |

| POP          | Direct           | (Direct) ← Stack Pointer SP                | Direct          | 2          | 2           |

| XCH          | Rn               | Exchange ACC with Rn                       | Register        | 1          | 1           |

|              | Direct           | Exchange ACC with Direct Byte              | Direct          | 2          | 1           |

|              | @Ri              | Exchange ACC with Indirect RAM             | Indirect        | 1          | 1           |

| XCHD         | A, @Ri           | Exchange ACC with Lower Order Indirect RAM | Indirect        | 1          | 1           |

# **Arithmetic Instructions**

Using Arithmetic Instructions, you can perform addition, subtraction, multiplication and division. The arithmetic instructions also include increment by one, decrement by one and a special instruction called Decimal Adjust Accumulator.

The Mnemonics associated with the Arithmetic Instructions of the 8051 Microcontroller Instruction Set are:

- ADD

- ADDC

- SUBB

- INC

- DEC

- MUL

- DIV

• DA A

The arithmetic instructions has no knowledge about the data format i.e. signed, unsigned, ASCII, BCD, etc. Also, the operations performed by the arithmetic instructions affect flags like carry, overflow, zero, etc. in the PSW Register.

All the possible Mnemonics associated with Arithmetic Instructions are mentioned in the following table.

| Mnemonic | Instruction | Description                                                                | Addressing Mode | # of Bytes | # of Cycles |

|----------|-------------|----------------------------------------------------------------------------|-----------------|------------|-------------|

| ADD      | A, #Data    | A ← A + Data                                                               | Immediate       | 2          | 1           |

|          | A, Rn       | $A \leftarrow A + Rn$                                                      | Register        | 1          | 1           |

|          | A, Direct   | A ← A + (Direct)                                                           | Direct          | 2          | 1           |

|          | A, @Ri      | A ← A + @Ri                                                                | Indirect        | 1          | 1           |

| ADDC     | A, #Data    | A ← A + Data + C                                                           | Immediate       | 2          | 1           |

|          | A, Rn       | $A \leftarrow A + Rn + C$                                                  | Register        | 1          | 1           |

|          | A, Direct   | $A \leftarrow A + (Direct) + C$                                            | Direct          | 2          | 1           |

|          | A, @Ri      | $A \leftarrow A + @Ri + C$                                                 | Indirect        | 1          | 1           |

| SUBB     | A, #Data    | A ← A – Data – C                                                           | Immediate       | 2          | 1           |

|          | A, Rn       | $A \leftarrow A - Rn - C$                                                  | Register        | 1          | 1           |

|          | A, Direct   | $A \leftarrow A - (Direct) - C$                                            | Direct          | 2          | 1           |

|          | A, @Ri      | $A \leftarrow A - @Ri - C$                                                 | Indirect        | 1          | 1           |

| MUL      | AB          | Multiply A with B<br>(A ← Lower Byte of A*B and B<br>← Higher Byte of A*B) |                 | 1          | 4           |

| DIV      | AB          | Divide A by B<br>(A ← Quotient and B ←<br>Remainder)                       |                 |            | 4           |

| DEC      | A           | A ← A – 1                                                                  | Register        | 1          | 1           |

| DLC      | Rn          | $Rn \leftarrow Rn - 1$                                                     | Register        | 1          | 1           |

|          | Direct      | $(Direct) \leftarrow (Direct) - 1$                                         | Direct          | 2          | 1           |

|          | @Ri         | @Ri ← @Ri – 1                                                              | Indirect        | 1          | i           |

| INC      | A           | A ← A + 1                                                                  | Register        | 1          | 1           |

|          | Rn          | $Rn \leftarrow Rn + 1$                                                     | Register        | 1          | 1           |

|          | Direct      | $(Direct) \leftarrow (Direct) + 1$                                         | Direct          | 2          | 1           |

|          | @Ri         | $(aRi \leftarrow aRi + 1)$                                                 | Indirect        | 1          | 1           |

|          | DPTR        | DPTR 		DPTR + 1                                                            | Register        | î          | 2           |

| DA       | A           | Decimal Adjust Accumulator                                                 |                 | 1          | 1           |

# **Logical Instructions**

The next group of instructions are the Logical Instructions, which perform logical operations like AND, OR, XOR, NOT, Rotate, Clear and Swap. Logical Instruction are performed on Bytes of data on a bit-by-bit basis.

Mnemonics associated with Logical Instructions are as follows:

- ANL

- ORL

- XRL

- CLR

- CPL

- RL

- RLC

- RR

- RRC

- SWAP

#### **VIDEOS SHARED WITH STUDENTS**

https://youtu.be/U6t6jZeseSc i/o port structure

https://youtu.be/Ok55KkwafQU memory organisation 8051

https://youtu.be/zzr0zLLeCQw Special function registers

<u>https://youtu.be/sLbw1stNkXM</u> Instruction set addressing modes

https://youtu.be/Vrazx7AsutM Assembler directives of 8051

https://youtu.be/0xHdq0QS1aQ Keypad interface with 8051 microcontroller